- Board development requires System-on-a-Chip (SoC) support. - The combined steps are listed - here. - The development steps for the board are listed below: -

-- Create the board directory as src/mainboard/<Vendor>/<Board>. -

- -- The following files are required to build a new board: -

-- Use the following steps to enable serial output: -

-- Memory timing data is located in the flash. This data is in the format of - serial presence detect - (SPD) data. - Use the following steps to load the SPD data: -

-- Ramstage's BS_DEV_ENUMERATE state displays the PCI vendor and device IDs for all - of the devices in the system. Edit the devicetree.cb file: -

-device pci 14.0 off endModified: 20 February 2016

- - diff --git a/Documentation/Intel/Board/galileo.html b/Documentation/Intel/Board/galileo.html deleted file mode 100644 index f7edf6e8ee..0000000000 --- a/Documentation/Intel/Board/galileo.html +++ /dev/null @@ -1,113 +0,0 @@ - - - - |

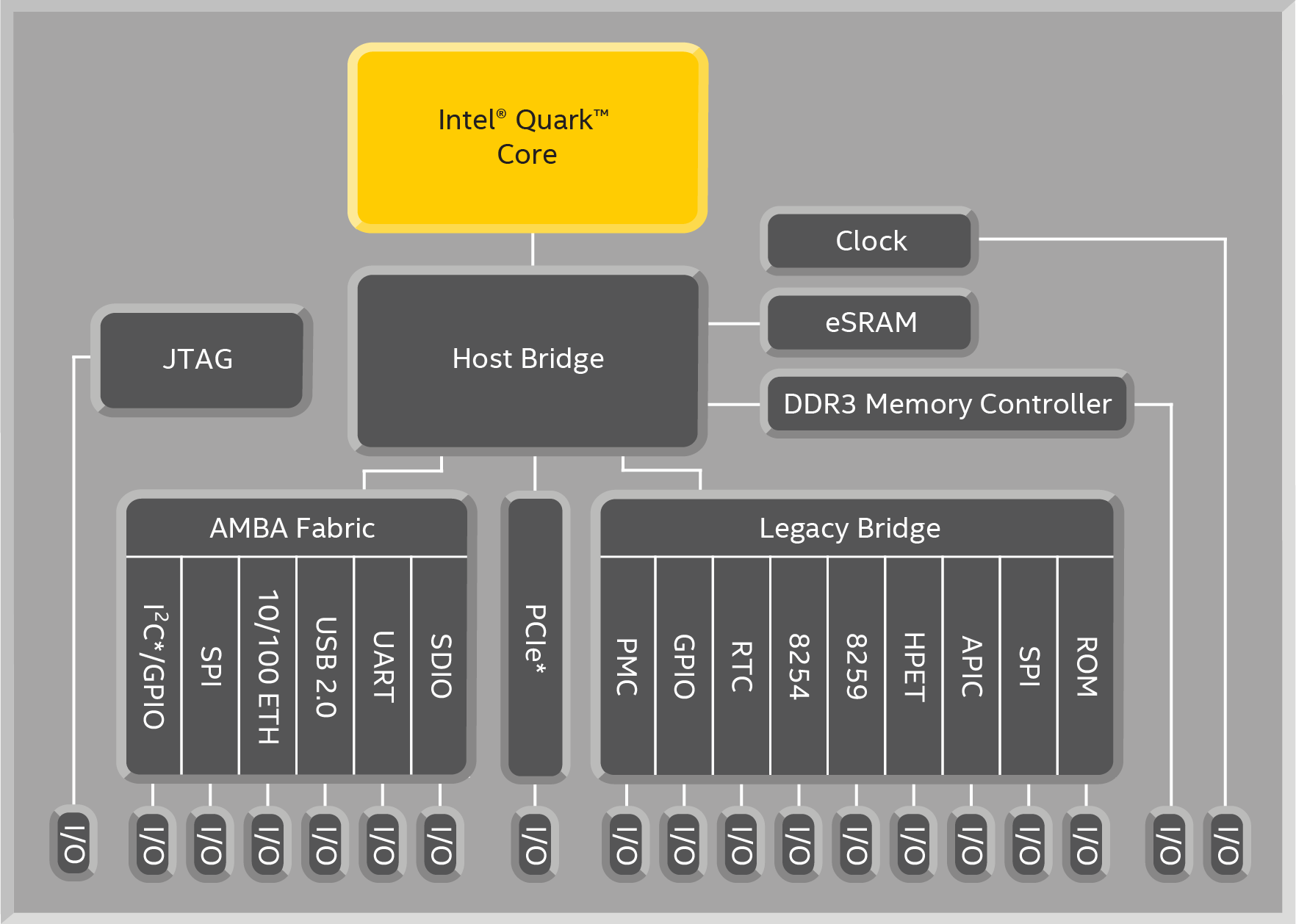

- - The Intel® Galileo Gen 2 mainboard code was developed along with the Intel® - Quark™ SoC: - - | -

Modified: 29 February 2016

- - diff --git a/Documentation/Intel/SoC/quark.html b/Documentation/Intel/SoC/quark.html deleted file mode 100644 index c3eead2e33..0000000000 --- a/Documentation/Intel/SoC/quark.html +++ /dev/null @@ -1,220 +0,0 @@ - - - - |

-

- The Quark™ SoC code was developed using the

- Galileo Gen 2

- board:

-

|

-

-Build Instructions: -

-build -p CorebootPayloadPkg/CorebootPayloadPkgIa32.dsc -a IA32 \

- -t GCC48 -b DEBUG -DDEBUG_PROPERTY_MASK=0x27 \

- -DDEBUG_PRINT_ERROR_LEVEL=0x80000042 -DSHELL_TYPE=BUILD_SHELL \

- -DMAX_LOGICAL_PROCESSORS=1

-ls Build/CorebootPayloadPkgIA32/DEBUG_GCC48/FV/UEFIPAYLOAD.fd

-build -p CorebootPayloadPkg\CorebootPayloadPkgIa32.dsc -a IA32 -t VS2015x86 -b DEBUG -DDEBUG_PROPERTY_MASK=0x27 -DDEBUG_PRINT_ERROR_LEVEL=0x80000042 -DSHELL_TYPE=BUILD_SHELL -DMAX_LOGICAL_PROCESSORS=1

-dir Build\CorebootPayloadPkgIA32\DEBUG_VS2015x86\FV\UEFIPAYLOAD.fd

-- Use the following steps to setup a build environment: -

-export WORKSPACE=$PWD

-export PACKAGES_PATH="$PWD/edk2:$PWD/edk2-non-osi"

-cd edk2

-export WORKSPACE=$PWD

-. edksetup.sh

-set WORKSPACE=%CD%

-set PACKAGES_PATH=%WORKSPACE%\edk2;%WORKSPACE%\edk2-non-osi

-set EDK_TOOLS_BIN=%WORKSPACE%\edk2-BaseTools-win32

-cd edk2

-edksetup.bat

--Getting the Quark FSP source: -

--There are two versions of FSP: FSP 1.1 and FSP 2.0. There are also two -different implementations of FSP, one using subroutines without SEC and -PEI core and the original implementation which relies on SEC and PEI core. -Finally there are two different build x86 types release (r32) and debug (d32). -

-Note that the subroutine implementations are a work in progress.

--Build commands shown building debug FSP: -

--There are some helper scripts to copy the FSP output into the coreboot -source tree. The parameters to these scripts are: -

--Script files: -

--Build Instructions: -

-build -p QuarkPlatformPkg/Quark.dsc -a IA32 -t GCC48 -b DEBUG -DDEBUG_PROPERTY_MASK=0x27 -DDEBUG_PRINT_ERROR_LEVEL=0x80000042

-ls Build/Quark/DEBUG_GCC48/FV/Quark.fd

-build -p QuarkPlatformPkg/Quark.dsc -a IA32 -t VS2012x86 -b DEBUG -DDEBUG_PROPERTY_MASK=0x27 -DDEBUG_PRINT_ERROR_LEVEL=0x80000042

-dir Build\Quark\DEBUG_VS2012x86\FV\Quark.fd

--Documentation: -

-Modified: 17 May 2016

- - diff --git a/Documentation/Intel/SoC/soc.html b/Documentation/Intel/SoC/soc.html deleted file mode 100644 index 8d565d52fe..0000000000 --- a/Documentation/Intel/SoC/soc.html +++ /dev/null @@ -1,730 +0,0 @@ - - - -- SoC development is best done in parallel with development for a specific - board. The combined steps are listed - here. - The development steps for the SoC are listed below: -

-- Create the directory as src/soc/<Vendor>/<Chip Family>. -

- -- The following files are required to build a new SoC: -

-- Some SoC parts require additional firmware components in the flash. - This section describes how to add those pieces. -

- -- The Intel Firmware Descriptor (IFD) is located at the base of the flash part. - The following command overwrites the base of the flash image with the Intel - Firmware Descriptor: -

-dd if=descriptor.bin of=build/coreboot.rom conv=notrunc >/dev/null 2>&1- Some SoC parts contain and require that the Management Engine (ME) be running - before it is possible to bring the x86 processor out of reset. A binary file - containing the management engine code must be added to the firmware using the - ifdtool. The following commands add this binary blob: -

-util/ifdtool/ifdtool -i ME:me.bin build/coreboot.rom

-mv build/coreboot.rom.new build/coreboot.rom

-- Early debugging between the reset vector and the time the serial port is enabled - is most easily done by writing values to port 0x80. -

- - -- When the reset vector is successfully invoked, port 0x80 will output the following value: -

-- Implement the bootblock using the following steps: -

-- Build Note: The following files are included into the default bootblock image: -

-- Enable the call to TempRamInit in two stages: -

--Use the following steps to locate the FSP binary: -

--Use the following steps to debug the call to TempRamInit: -

-util/cbfstool/cbfstool build/coreboot.rom add -t microcode -n cpu_microcode_blob.bin -b <base address> -f cpu_microcode_blob.bin- The following steps add the serial output support for romstage: -

-- The following steps implement the code to get the previous sleep state: -

-- The following steps implement the code to support the FSP MemoryInit call: -

-- Build Note: The src/mainboard/<Vendor>/<Board>/devicetree.cb - file specifies the default values for these parameters. The build - process creates the static.c module which contains the config data - structure containing these values. -

-- A shadow of the SPI flash part is mapped from 0x000e0000 to 0x000fffff. - This shadow needs to be disabled to allow RAM to properly respond to - this address range. -

-- The src/mainboard/<Vendor>/<Board>/devicetree.cb file drives the - execution during ramstage. This file is processed by the util/sconfig utility - to generate build/mainboard/<Vendor>/<Board>/static.c. The various - state routines in - src/lib/hardwaremain.c - call dev_* routines which use the tables in static.c to locate operation tables - associated with the various chips and devices. After location the operation - tables, the state routines call one or more functions depending upon the - state of the state machine. -

- -- Kick-starting the ramstage state machine requires creating the operation table - for the chip listed in devicetree.cb: -

-- coreboot uses the domain operation table to initiate operations on all of the - devices in the domain. By default coreboot enables all PCI devices which it - finds. Listing a device in devicetree.cb gives the board vendor control over - the device state. Non-PCI devices may also be listed under PCI device such as - the LPC bus or SMbus devices. -

-static struct device_operations pci_domain_ops = {

- .read_resources = pci_domain_read_resources,

- .set_resources = pci_domain_set_resources,

- .scan_bus = pci_domain_scan_bus,

-};

- if (dev->path.type == DEVICE_PATH_DOMAIN) {

- dev->ops = &pci_domain_ops;

- }

-- PCI device drivers consist of a ".c" file which contains a "pci_driver" data - structure at the end of the file with the attribute tag "__pci_driver". This - attribute tag places an entry into a link time table listing the various - coreboot device drivers. -

-- Specify the following fields in the table: -

-- PCI subsystem IDs are assigned during the BS_DEV_ENABLE state. The device - driver may use the common mechanism to assign subsystem IDs by adding - the ".ops_pci" to the pci_driver data structure. This field points to - a "struct pci_operations" that specifies a routine to set the subsystem - IDs for the device. The routine might look something like this: -

-static void pci_set_subsystem(struct device *dev, unsigned vendor, unsigned device)

-{

- if (!vendor || !device) {

- vendor = pci_read_config32(dev, PCI_VENDOR_ID);

- device = vendor >> 16;

- }

- printk(BIOS_SPEW,

- "PCI: %02x:%02x:%d subsystem vendor: 0x%04x, device: 0x%04x\n",

- 0, PCI_SLOT(dev->path.pci.devfn), PCI_FUNC(dev->path.pci.devfn),

- vendor & 0xffff, device);

- pci_write_config32(dev, PCI_SUBSYSTEM_VENDOR_ID,

- ((device & 0xffff) << 16) | (vendor & 0xffff));

-}

-- The memory map is built by the various PCI device drivers during the - BS_DEV_RESOURCES state of ramstage. The northcluster driver will typically - specify the DRAM resources while the other drivers will typically specify - the IO resources. These resources are hung off the struct device *data structure by - src/device/device_util.c/new_resource. -

-- During the BS_WRITE_TABLES state, coreboot collects these resources and - places them into a data structure identified by LB_MEM_TABLE. -

-- Edit the device driver file: -

-- Testing: Verify that the resources are properly displayed by coreboot during the BS_WRITE_TABLES state. -

- - - -- One of the payloads that needs ACPI tables is the EDK2 CorebootPayloadPkg. -

- -- The EDK2 module - CorebootModulePkg/Library/CbParseLib/CbParseLib.c - requires that the FADT contains the values in the table below. - These values are placed into a HOB identified by - gUefiAcpiBoardInfoGuid - by routine - CorebootModulePkg/CbSupportPei/CbSupportPei/CbPeiEntryPoint. -

-| coreboot Field | -EDK2 Field | -gUefiAcpiBoardInfoGuid | -Use - | - ACPI Spec. - Section - | -

| gpe0_blk gpe0_blk_len |

- Gpe0Blk Gpe0BlkLen |

- - PmGpeEnBase - | -Shutdown | -4.8.4.1 | -

| pm1a_cnt_blk | -Pm1aCntBlk | -PmCtrlRegBase | -

- Shutdown - Suspend - |

- 4.8.3.2.1 | -

| pm1a_evt_blk | -Pm1aEvtBlk | -PmEvtBase | -Shutdown | -4.8.3.1.1 | -

| pm_tmr_blk | -PmTmrBlk | -PmTimerRegBase | -- Timer - | -4.8.3.3 | -

| reset_reg. | -ResetReg.Address | -ResetRegAddress | -- Cold - and - Warm - resets - | -4.3.3.6 | -

| reset_value | -ResetValue | -ResetValue | -- Cold - and - Warm - resets - | -4.8.3.6 | -

- The EDK2 data structure is defined in - MdeModulePkg/Include/IndustryStandard/Acpi61.h - The coreboot data structure is defined in - src/arch/x86/include/arch/acpi.h -

- -- One of the payloads that needs legacy hardare is the EDK2 CorebootPayloadPkg. -

- -| Peripheral | -Use | -8259 Interrupt Vector | -IDT Base Offset | -Interrupt Handler | -

|---|---|---|---|---|

| - 8254 - Programmable Interval Timer - | -- EDK2: PcAtChipsetPkg/8254TimerDxe/Timer.c - | -0 | -0x340 | -- TimerInterruptHandler - | -

| - 8259 - Programmable Interrupt Controller - | -- EDK2: PcAtChipsetPkg/8259InterruptControllerDxe/8259.c - | -

- Master interrupts: 0, 2 - 7 - Slave interrupts: 8 - 15 - Interrupt vector 1 is never generated, the cascaded input generates interrupts 8 - 15 - |

-

- Master: 0x340, 0x350 - 0x378 - Slave: 0x380 - 0x3b8 - Interrupt descriptors are 8 bytes each - |

- - |

Modified: 4 March 2016

- - diff --git a/Documentation/Intel/development.html b/Documentation/Intel/development.html deleted file mode 100644 index 92b1d4be8d..0000000000 --- a/Documentation/Intel/development.html +++ /dev/null @@ -1,377 +0,0 @@ - - - -- The x86 development process for coreboot is broken into the following components: -

- -- The development process has two main phases: -

-- The combined steps below describe how to bring up a minimal coreboot for a - system-on-a-chip (SoC) and a development board: -

-| The initial coreboot steps are single threaded! - The initial minimal FSP development is also single threaded. - Progress can speed up by adding more developers after the minimal coreboot/FSP - implementation reaches the payload. - | -

sudo apt-get install m4 bison flex libncurses5-dev

-make crossgcc-i386make crossgcc-i386 CPUS=N- Most of the coreboot development gets done in this phase. Implementation tasks in this - phase are easily done in parallel. -

-Features |

- ||

|---|---|---|

| SoC | -Where | -Testing | -

| 8254 Programmable Interval Timer | -Legacy hardware support | -CorebootPayloadPkg gets to shell prompt | -

| 8259 Programmable Interrupt Controller | -Legacy hardware support | -CorebootPayloadPkg gets to shell prompt | -

| Cache-as-RAM | -

- Find

- FSP binary:

- cache_as_ram.inc - Enable: FSP 1.1 TempRamInit - called from - cache_as_ram.inc - Disable: FSP 1.1 TempRamExit called from - after_raminit.S - |

- FindFSP: POST code 0x90

- (POST_FSP_TEMP_RAM_INIT)

- is displayed - Enable: POST code - 0x2A - is displayed - Disable: CONFIG_DISPLAY_MTRRS=y, MTRRs displayed after call to TempRamExit - |

-

| Memory Map | -- Implement a device driver for the - north cluster - | -coreboot displays the memory map correctly during the BS_WRITE_TABLES state | -

| MTRRs | -

- Set values: src/drivers/intel/fsp1_1/stack.c/setup_stack_and_mtrrs - Load values: src/drivers/intel/fsp1_1/after_raminit.S - |

- Set: Post code 0x91

- (POST_FSP_TEMP_RAM_EXIT)

- is displayed by

- after_raminit.S - Load: Post code 0x3C is displayed by - after_raminit.S - and CONFIG_DISPLAY_MTRRS=y displays the correct memory regions |

-

| PCI Device Support | -Implement a PCI device driver | -The device is detected by coreboot and usable by the payload | -

| Ramstage state machine | -- Implement the chip and domain operations to start the - device tree - processing - | -- During the BS_DEV_ENUMERATE state, ramstage now display the device IDs - for the PCI devices on the bus. - | -

| ROM Shadow 0x000E0000 - 0x000FFFFF |

- - Disable: src/soc/<Vendor>/<Chip Family>/romstage/romstage.c/soc_after_ram_init routine - | -Operates as RAM: Writes followed by a read to the 0x000E0000 - 0x000FFFFF region returns the value written | -

| Board | -Where | -Testing | -

| Device Tree | -

- List PCI vendor and device IDs by starting

- the device tree processing - Disable PCI devices - Enable: Implement a PCI device driver - |

- List: BS_DEV_ENUMERATE state displays PCI vendor and device IDs - Disable: BS_DEV_ENUMERATE state shows the devices as disabled - Enable: BS_DEV_ENUMERATE state shows the device as on and the device works for the payload - |

-

| DRAM | -

- Load SPD data: src/soc/mainboard/<Vendor>/<Board>/spd/spd.c - UPD Setup: -

|

- Select the following Kconfig values

-

|

-

| Serial Port | -

- SoC Support - Enable: src/soc/mainboard/<Board>/com_init.c/car_mainboard_pre_console_init - |

- Debug serial output works | -

| Payload | -Where | -Testing | -

| ACPI Tables | -

- SoC Support - |

- Verified by payload or OS | -

| FSP | -Where | -Testing | -

| TempRamInit | -FSP TempRamInit | -FSP binary found: POST code 0x90

- (POST_FSP_TEMP_RAM_INIT)

- is displayed - TempRamInit successful: POST code - 0x2A - is displayed - |

-

| MemoryInit | -SoC support - Board support - |

- Select the following Kconfig values

-

|

-

| TempRamExit | -src/drivers/intel/fsp1_1/after_raminit.S | -Post code 0x91

- (POST_FSP_TEMP_RAM_EXIT)

- is displayed before calling TempRamExit by

- after_raminit.S,

- CONFIG_DISPLAY_MTRRS=y displays the correct memory regions and

- Post code 0x39 is displayed by

- after_raminit.S - |

-

| SiliconInit | -- Implement the .init routine for the - chip operations structure - | -During BS_DEV_INIT_CHIPS state, SiliconInit gets called and returns 0x00000000 | -

| FspNotify | -- The code which calls FspNotify is located in - src/drivers/intel/fsp1_1/fsp_util.c. - The fsp_notify_boot_state_callback routine is called three times as specified - by the BOOT_STATE_INIT_ENTRY macros below the routine. - | -

- The FspNotify routines are called during:

-

|

-

Modified: 4 March 2016

- - diff --git a/Documentation/Intel/fsp1_1.html b/Documentation/Intel/fsp1_1.html deleted file mode 100644 index 94cb6bf8be..0000000000 --- a/Documentation/Intel/fsp1_1.html +++ /dev/null @@ -1,79 +0,0 @@ - - - -- Firmware Support Package (FSP) integration requires System-on-a-Chip (SoC) - and board support. The combined steps are listed - here. - The development steps for FSP are listed below: -

-- FSP Documentation: -

-- Add the FSP binary to the coreboot flash image using the following command: -

-util/cbfstool/cbfstool build/coreboot.rom add -t fsp -n fsp.bin -b <base address> -f fsp.bin- This command relocates the FSP binary to the 4K byte aligned location in CBFS so that the - FSP code for TempRamInit may be executed in place. -

- - -- Set the following Kconfig values: -

-Modified: 17 May 2016

- - diff --git a/Documentation/Intel/index.html b/Documentation/Intel/index.html deleted file mode 100644 index 9d8aad05e9..0000000000 --- a/Documentation/Intel/index.html +++ /dev/null @@ -1,128 +0,0 @@ - - - -| Feature/Specification | Linux View/Test | EDK-II View/Test |

|---|---|---|

| e820 | -dmesg | -- |

| ACPI | -acpidump | -- |

| EDID | -get-edid | parse-edid | -- |

| I2C | -i2cdetect | -- |

| Multiprocessor | -lscpu | -- |

| PCI | -lspci | -pci | -

| SMBIOS | -dmidecode | -smbiosview | -

| USB | -lsusb | -- |

Modified: 18 June 2016

- -