### Faculté des Sciences et Ingénierie Master Informatique Systèmes Électroniques, Systèmes Informatiques

Laboratoire d'Informatique Paris 6 - CIAN

### Hardware initialization of modern computers

A review on the importance of firmware in modern computing and a documentation on the Asus KGPE-D16 RAM initialization

August, 2024

Adrien 'neox' Bourmault (neox@gnu.org)

### **Acknowledgments**

First and foremost, I would like to express my deep gratitude to Marie-Minerve Louërat, without whom this work would not have come to fruition. Her efforts to assist me on legal matters and our enriching discussions on the philosophy of free software have been invaluable to me.

I am also thankful to Roselyne Chotin for agreeing to fund this work as without her support, none of this would have been possible, and Franck Wajsburt for his invaluable advice at the beginning of my work, which greatly helped me organize myself, as well as for his support and reviews throughout this period.

I wish to express my appreciation to the Free Software Foundation for funding the necessary equipment for this project. Special thanks go to Zoë Kooymann and Ian Kelling for their dedication in securing this funding and for their kindness throughout all the procedures.

I am deeply grateful to Denis Carikli (GNUtoo), my fellow GNU Boot co-maintainer, for his meticulous reviews, emotional support, and brilliant ideas that enriched this work, and to Richard M. Stallman for his advice and support throughout this journey.

A big thank you to Manuel Bouyer for his infinite patience with all my requests regarding network, software, and hardware configurations.

Also, I warmly thank my family and friends for their constant encouragement and for reviewing my work throughout this entire process.

And finally, I would like to thank the break room and its kettle, without which no tea would have been possible, thereby jeopardizing this work.

### **Abstract**

The global trend is towards the scarcity of free software-compatible hardware, and soon there will be no computer that will work without software domination by big companies, especially involving firmware like BIOSes.

A Basic Input Output System (BIOS) was originally a set of low-level functions contained in the read-only memory of a computer's mainboard, enabling it to perform basic operations when powered up. However, the definition of a BIOS has evolved to include what used to be known as Power On Self Test (POST) for the presence of peripherals, allocating resources for them to avoid conflicts, and then handing over to an operating system boot loader. Nowadays, the bulk of the BIOS work is the initialization and training of RAM. This means, for example, initializing the memory controller and optimizing timing and read/write voltage for optimal performance, making the code complex, as its role is to optimize several parallel buses operating at high speeds and shared by many CPU cores, and make them act as a homogeneous whole.

This document is the product of a project hosted by the *LIP6 laboratory* and supported by the *GNU Boot Project* and the *Free Software Foundation*. It delves into the importance of firmware in the hardware initialization of modern computers and explores various aspects of firmware, such as Intel Management Engine (ME), AMD Platform Security Processor (PSP), Advanced Configuration and Power Interface (ACPI), and System Management Mode (SMM). Additionally, it provides an in-depth look at memory initialization and training algorithms, highlighting their critical role in system stability and performance. Examples of the implementation in the ASUS KGPE-D16 mainboard are presented, describing its hardware characteristics, topology, and the crucial role of firmware in its operation after the mainboard architecture is examined. Practical examples illustrate the impact of firmware on hardware initialization, memory optimization, resource allocation, power management, and security. Specific algorithms used for memory training and their outcomes are analyzed to demonstrate the complexity and importance of firmware in achieving optimal system performance. Furthermore, this document explores the relationship between firmware and hardware virtualization. Security considerations and future trends in firmware development are also addressed, emphasizing the need for continued research and advocacy for free software-compatible hardware.

### **Contents**

| Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                              | 3  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4  |

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5  |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                              | 7  |

| List of Listings                                                                                                                                                                                                                                                                                                                                                                                                                             | g  |

| 1 Introduction to firmware and BIOS evolution                                                                                                                                                                                                                                                                                                                                                                                                | 10 |

| 1.1 Historical context of BIOS 1.1.1 Definition and origin 1.1.2 Functionalities and limitations 1.2 Modern BIOS and UEFI 1.2.1 Transition from traditional BIOS to UEFI (Unified Extensible Firmware Interface) 1.2.2 An other way with coreboot 1.3 Shift in firmware responsibilities  2 Characteristics of ASUS KGPE-D16 mainboard 2.1 Overview of ASUS KGPE-D16 hardware 2.2 Chipset 2.3 Processors 2.4 Baseboard Management Controller |    |

| 3 Key components in modern firmware                                                                                                                                                                                                                                                                                                                                                                                                          | 22 |

| 3.1 General structure of coreboot  3.1.1 Bootblock  3.1.2 Romstage  3.1.3 Ramstage  3.1.3.1 Advanced Configuration and Power Interface  3.1.3.2 System Management Mode  3.1.4 Payload                                                                                                                                                                                                                                                        |    |

| 3.2 AMD Platform Security Processor and Intel Management Engine                                                                                                                                                                                                                                                                                                                                                                              | 28 |

| 4 Me    | emory initialization and training                                | 30 |

|---------|------------------------------------------------------------------|----|

| 4.1     | Importance of DDR3 memory initialization                         | 30 |

| 4.2     | General steps for DDR3 configuration                             | 31 |

| 4.3     | Memory initialization techniques                                 | 34 |

| 4.3.1   |                                                                  |    |

| 4.3.2   | BIOS and Kernel Developer Guide (BKDG) recommendations           | 35 |

| 4.3     | 3.2.1 DDR3 initialization procedure                              | 36 |

| 4.3     | 3.2.2 ZQ calibration process                                     |    |

| 4.3     | 3.2.3 Write leveling process                                     | 37 |

| 4.4     | Current implementation and potential improvements                | 39 |

| 4.4.1   | Current implementation in coreboot on the KGPE-D16               | 39 |

| 4.4     | 4.1.1 Details on the DQS training function                       | 41 |

| 4.4     | 1.1.2 Details on the write leveling implementation               | 43 |

| 4.4     | 1.1.3 Details on the DQS position training function              | 45 |

| 4.4     | 1.1.4 Details on the DQS receiver training function              | 47 |

| 4.4.2   | Potential enhancements                                           | 50 |

| 4.4     | 4.2.1 DQS receiver training                                      | 50 |

| 4.4     | 4.2.2 Write leveling                                             | 52 |

| 4.4     | 1.2.3 DQS position training                                      | 54 |

| 4.4     | 1.2.4 On saving training values in NVRAM                         | 56 |

| 4.4     | 1.2.5 A seedless DQS position training algorithm                 | 57 |

|         | tualization of the operating system through firmware abstraction | 59 |

| 5.1     | ACPI and abstraction of hardware control                         |    |

| 5.2     | SMM as a hidden execution layer                                  | 60 |

| 5.3     | UEFI and persistence                                             | 60 |

| 5.3.1   | Memory Management                                                | 61 |

| 5.3.2   | Pile System Management                                           | 61 |

| 5.3.3   | Device Drivers                                                   | 61 |

| 5.3.4   | Power Management                                                 | 61 |

| 5.4     | Intel and AMD: control beyond the OS                             | 61 |

| 5.5     | The OS as a virtualized environment                              | 62 |

| Conclu  | usion                                                            | 63 |

| Bibliog | graphy                                                           | 70 |

| Appen   | dix: Long code listings                                          | 71 |

| GNU (   | General Public License version 2                                 | 82 |

| GNU F   | Free Documentation License                                       | 87 |

# List of Figures

| 1.1 | The eight-striped wordmark of IBM (1967, public domain, trademarked)                       | 10 |

|-----|--------------------------------------------------------------------------------------------|----|

| 1.2 | An AMI BIOS chip from a Dell 310, by Jud McCranie (CC BY-SA 4.0, 2018)                     | 11 |

|     | The UEFI logo (public domain, 2010)                                                        |    |

|     | The coreboot logo, by Konsult Stuge & coresystems (coreboot logo license, 2008)            |    |

| 1.5 | The GNU Boot logo, by Jason Self (CC0, 2020)                                               | 13 |

| 2.1 | The KGPE-D16 (CC BY-SA 4.0, 2021)                                                          | 15 |

| 2.2 | Basic schematics of the ASUS KGPE-D16 Mainboard, ASUS (2011)                               | 16 |

| 2.3 | The KGPE-D16, viewed from the top (CC BY-SA 4.0, 2024)                                     | 17 |

| 2.4 | Functional diagram presenting the IOAPIC function of the SP5100, ASUS (2011)               | 18 |

| 2.5 | Functional diagram of the KGPE-D16 chipset (CC BY-SA 4.0, 2024)                            | 18 |

| 2.6 | Annotated photography of an Opteron 6200 series CPU (2024), from a photography by AMD Inc. |    |

|     | (2008)                                                                                     | 19 |

| 2.7 | Functional diagram of an Opteron 6200 package (CC BY-SA 4.0, 2024)                         |    |

| 3.1 | coreboot's stages timeline, by coreboot project (CC BY-SA 4.0, 2009)                       | 22 |

| 3.2 | coreboot ROM architecture (CC BY-SA 4.0, 2024)                                             |    |

| 4.1 | DDR3 fly-by versus T-topology (CC BY-SA 4.0, 2021)                                         | 31 |

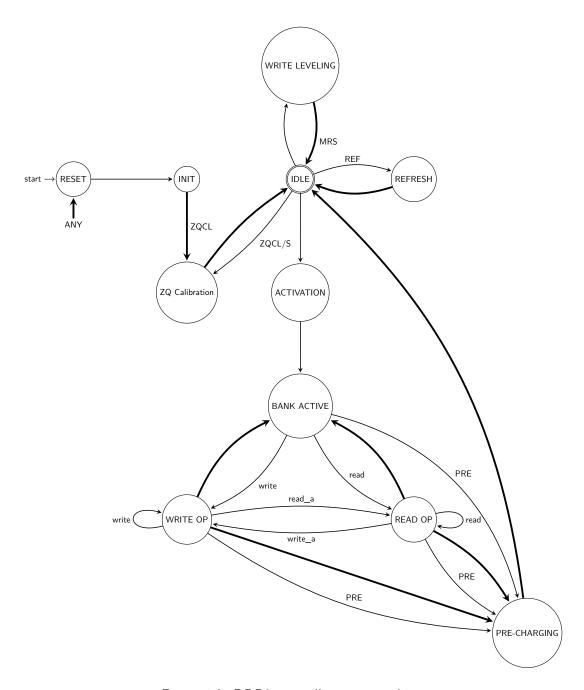

|     | DDR3 controller state machine                                                              |    |

## **List of Listings**

| 4.1         | fill_mem_ctrl(), extract from src/northbridge/amd/amdfam10/raminit_sysinfo_in_                                                                   |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2         | ram.c                                                                                                                                            |

| 12          | mct_ddr3/mct_d.c                                                                                                                                 |

| 4.3         | Setting initial TCWL offset to zero for all nodes and DCTs, extract from the DQSTiming_D function in src/northbridge/amd/amdmct/mct_ddr3/mct_d.c |

| 4.4         | Retry mechanism initialization and pre-training operations, extract from the DQSTiming_D function in src/northbridge/amd/amdmct/mct_ddr3/mct_d.c |

| 4.5         | PHY compensation initialization, extract from the DQSTiming_D function in src/northbridge/amd/amdmct/mct_ddr3/mct_d.c                            |

| 4.6         | Main DQS training process in multiple passes, extract from the DQSTiming_D function in src/northbridge/amd/amdmct/mct_ddr3/mct_d.c               |

| 4.7         | Post-training cleanup and final hook execution, extract from the DQSTiming_D function in src/northbridge/amd/amdmct/mct_ddr3/mct_d.c             |

| 4.8         | Write leveling (first pass), extract from the WriteLevelization_HW function in src/ northbridge/amd/amdmct/mct_ddr3/mcthwl.c                     |

| 4.9         | Target DIMM selection for write leveling, extract from AgesaHwWlPhase1 function in src/                                                          |

| 7.5         | northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                                                                                        |

| 4.10        | Handling of x4 DIMMs and nibble training, extract from AgesaHwWlPhase1 function in src/                                                          |

| 0           | northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                                                                                        |

| 4.11        | Preparing DIMMs for write leveling, extract from AgesaHwWlPhase1 function in src/                                                                |

|             | northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                                                                                        |

| 4.12        | Seed generation, extract from procConfig function in src/northbridge/amd/amdmct/mct_                                                             |

|             | ddr3/mhwlc_d.c                                                                                                                                   |

| 4.13        | Initiating write leveling training, extract from AgesaHwWlPhase1 function in src/northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                       |

| 4.14        | Exit for non-x4 DIMMs, extract from AgesaHwWlPhase2 function in src/northbridge/amd/ amdmct/mct_ddr3/mhwlc_d.c                                   |

| <i>4</i> 15 | Reading and storing delay values after write leveling, extract from AgesaHwWlPhase2 function in                                                  |

| 7.13        | src/northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                                                                                    |

| 4 16        | Looping over each receiver, extract from TrainDQSRdWrPos_D_Fam15 function in src/                                                                |

|             | northbridge/amd/amdmct/mct_ddr3/mctdqs_d.c                                                                                                       |

| 4.17        | Iteration over write and read delay values for each lane, extract from TrainDQSRdWrPos_D_Fam15                                                   |

|             | function in src/northbridge/amd/amdmct/mct_ddr3/mctdqs_d.c                                                                                       |

| 4.18        | Processing the results to determine the best DQS delay settings, extract from TrainDQSRdWrPos_                                                   |

|             | D_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mctdqs_d.c                                                                               |

| 4.19        | Final error handling and return value, extract from TrainDQSRdWrPos_D_Fam15 function in src/                                                     |

|             | northbridge/amd/amdmct/mct_ddr3/mctdqs_d.c                                                                                                       |

| 4.20        | Adjusting the seed values based on the operating frequency of the memory, extract from                                                           |

|             | dqsTrainRcvrEn_SW_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mctsrc.c 49                                                              |

| 4.21        | Setting initial delay values based on the generated seed values, extract from dqsTrainRcvrEn_                                                    |

|             | SW_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mctsrc.c                                                                                |

| 4.22        | Initialization phase: Enabling training mode and disabling ECC, extract from dqsTrainRcvrEn_                                                     |

|             | SW_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mctsrc.c                                                                                |

| 4.23        | Iterating over ranks and nibbles to apply delay values, extract from dqsTrainRcvrEn_SW_Fam15                                                     |

|             | function in src/northbridge/amd/amdmct/mct_ddr3/mctsrc.c50                                                                                       |

| 4.24        | Exiting training mode and setting read latency, extract from dqsTrainRcvrEn_SW_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mctsrc.c                                   | 50   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.25        | An unimplemented feature in the seed adjustment logic, extract from dqsTrainRcvrEn_SW_Fam15                                                                                     |      |

|             | <pre>function in src/northbridge/amd/amdmct/mct_ddr3/mcrsrc.c</pre>                                                                                                             | . 51 |

|             | LRDIMM support is unimplemented, extract from dqsTrainRcvrEn_SW_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mcrsrc.c                                                  | . 51 |

| 4.27        | Questioning the use of SSEDIS in the MSR setting, extract from dqsTrainRcvrEn_SW_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mcrsrc.c                                 | . 51 |

| 4.28        | A possible misprint in the BKDG regarding delay settings, extract from dqsTrainRcvrEn_SW_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mcrsrc.c                         | . 52 |

| 4.29        | Seeds used for DQS Receiver training, extract from dqsTrainRcvrEn_SW_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mcrsrc.c                                             | . 53 |

| 4.30        | Complex seed adjustment logic, extract from dqsTrainRcvrEn_SW_Fam15 function in src/northbridge/amd/amdmct/mct_ddr3/mcrsrc.c                                                    | . 53 |

| 4.31        | Incomplete seed generation implementation, extract from procConfig function in src/northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                                    |      |

| 4.32        | Omission of WrDqDqsEarly parameter, extract from procConfig function in src/northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                                           |      |

| 4.33        | Lack of mainboard-specific seed overrides, extract from procConfig function in src/northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                                    |      |

| 4.34        | Disabled CGD adjustment due to conflicts, extract from AgesaHwWlPhase2 function in src/northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                                |      |

| 4.35        | Bypass of critical adjustments during speed tuning, extract from AgesaHwWlPhase2 function in src/northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                      |      |

| 4.36        | Blunt error handling to compensate for noise and instability, extract from AgesaHwWlPhase2                                                                                      |      |

| 4.37        | function in src/northbridge/amd/amdmct/mct_ddr3/mhwlc_d.c                                                                                                                       |      |

| <b>5</b> 00 | function in src/northbridge/amd/amdmct/mct_ddr3/mctdqs_d.c                                                                                                                      |      |

|             | How to estimate the impact of ACPICA in Linux                                                                                                                                   | . 59 |

| L.1         | Beginning of mctAutoInitMCT_D(), extract from src/northbridge/amd/amdmct/mct_ddr3/mct_d.c                                                                                       | . 72 |

| L.2         | DIMM initialization in mctAutoInitMCT_D(), extract from src/northbridge/amd/amdmct/mct_ddr3/mct_d.c                                                                             | . 73 |

| L.3         | Voltage control in mctAutoInitMCT_D(), extract from src/northbridge/amd/amdmct/mct_ddr3/mct_d.c                                                                                 | . 74 |

| L.4         | <pre>mctAutoInitMCT_D() does not allow restoring previous training values, extract from src/<br/>northbridge/amd/amdmct/mct_ddr3/mct_d.c</pre>                                  | . 75 |

| L.5         | Preparing SMBus, DCTs and NB in mctAutoInitMCT_D() from src/northbridge/amd/amdmct/mct_ddr3/mct_d.c                                                                             | . 76 |

| L.6         | Get DQS, reset and activate ECC in mctAutoInitMCT_D() from src/northbridge/amd/amdmct/mct_ddr3/mct_d.c                                                                          | . 77 |

| L.7         | Mapping DRAM with cache, validating DCT nodes and finishing the init process in mctAutoInitMCT_D() from src/northbridge/amd/amdmct/mct_ddr3/mct_d.c                             | . 78 |

| L.8         | Error detection and retry mechanism during DQS training, extract from the DQSTiming_D function in src/northbridge/amd/amdmct/mct_ddr3/mct_d.c                                   | . 79 |

| L.9         | Write Leveling (second pass), extract from the WriteLevelization_HW function in src/northbridge/amd/amdmct/mct_ddr3/mcthwl.c                                                    |      |

| L.10        | Seed generation for DQS receiver enable training based on DIMM type and configuration, extract from fam15_receiver_enable_training_seed function in src/northbridge/amd/amdmct/ | . 00 |

|             | mct_ddr3/mctsrc.c                                                                                                                                                               | . 81 |

### Chapter 1

### Introduction to firmware and BIOS evolution

#### 1.1 Historical context of BIOS

### 1.1.1 Definition and origin

The BIOS (Basic Input/Output System) is firmware, which is a type of software that is embedded into hardware devices to control their basic functions, acting as a bridge between hardware and other software, ensuring that the hardware operates correctly. Unlike regular software, firmware is usually stored in a non-volatile memory like ROM or flash memory. The term "firmware" comes from its role: it is "firm" because it's more permanent than regular software (which can be easily changed) but not as rigid as hardware.

The BIOS is used to perform initialization during the booting process and to provide runtime services for operating systems and programs. Being a critical component for the startup of personal computers, acting as an intermediary between the computer's hardware and its operating system, the BIOS is embedded on a chip on the motherboard and is the first code that runs when a PC is powered on. The concept of BIOS has its roots in the early days of personal computing. It was first developed by IBM for their IBM PC, which was introduced in 1981 [45]. The term BIOS itself was coined by Gary Kildall, who developed the CP/M (Control Program for Microcomputers) operating system [98]. In CP/M, BIOS was used to describe a component that interfaced directly with the hardware, allowing the operating system to be somewhat hardware-independent.

Figure 1.1: The eight-striped wordmark of IBM (1967, public domain, trademarked)

IBM's implementation of BIOS became a de facto standard in the industry, as it was part of the IBM PC's open architecture [48][15], which refers to the design philosophy adopted by IBM when developing the IBM Personal Computer (PC), introduced in 1981. This architecture is characterized by the use of off-the-shelf components and publicly available specifications, which allowed other manufacturers to create compatible hardware and software. It was in fact a departure from the proprietary systems prevalent at the time, where companies closely guarded their designs to maintain control over the hardware and software ecosystem. For example, IBM used the Intel 8088 CPU, a well-documented and widely available processor, and also the Industry Standard Architecture (ISA) bus, which defined how various components like memory, storage, and peripherals communicated with the CPU. This open architecture allowed other manufacturers to create IBM-compatible computers, also known as "clones", which further popularized the BIOS concept. As a result, the IBM PC BIOS set the stage for a standardized method of interacting with computer hardware, which has evolved over the years but remains fundamentally the same in principle. IBM also published detailed technical documentation at that time, including circuit diagrams,

BIOS listings, and interface specifications. This transparency allowed other companies to understand and replicate the IBM PC's functionality [45].

#### 1.1.2 Functionalities and limitations

When a computer is powered on, the BIOS executes a Power-On Self-Test (POST), a diagnostic sequence that verifies the integrity and functionality of critical hardware components such as the CPU, RAM, disk drives, keyboard, and other peripherals [116]. This process ensures that all essential hardware components are operational before the system attempts to load the operating system. If any issues are detected, the BIOS generates error messages or beep codes to alert the user. Following the successful completion of POST, the BIOS runs the bootstrap loader, a small program that identifies the operating system's bootloader on a storage device, such as a hard drive, floppy disk, or optical drive. The bootstrap loader then transfers control to the OS bootloader, initiating the process of loading the operating system into the computer's memory and starting it. This step effectively bridges the gap between hardware initialization and operating system execution. The BIOS also provides a set of low-level software routines known as interrupts. These routines enable software to perform basic input/output operations, such as reading from the keyboard, writing to the display, and accessing disk drives, without needing to manage the hardware directly. By providing standardized interfaces for hardware components, the BIOS simplifies software development and improves compatibility across different hardware configurations [15].

Figure 1.2: An AMI BIOS chip from a Dell 310, by Jud McCranie (CC BY-SA 4.0, 2018)

Despite its essential role, the early BIOS had several limitations. One significant limitation was its limited storage capacity. Early BIOS firmware was stored in Read-Only Memory (ROM) chips with very limited storage, often just a few kilobytes. This constrained the complexity and functionality of the BIOS, limiting it to only the most essential tasks needed to start the system and provide basic hardware control. The original BIOS was also non-extensible. ROM chips were typically soldered onto the motherboard, making updates difficult and costly. Bug fixes, updates for new hardware support, or enhancements required replacing the ROM chip, leading to challenges in maintaining and upgrading systems. Furthermore, the early BIOS was tailored for the specific hardware configurations of the initial IBM PC models, which included a limited set of peripherals and expansion options. As new hardware components and peripherals were developed, the BIOS often needed to be updated to support them, which was not always feasible or timely. Performance bottlenecks were another limitation. The BIOS provided basic input/output operations that were often slower than direct hardware access methods. For example, disk I/O operations through BIOS interrupts were slower compared to later direct access methods provided by operating systems, resulting in performance bottlenecks, especially for disk-intensive operations [14]. Early BIOS implementations also had minimal security features. There were no mechanisms to verify the integrity of the BIOS code or to protect against unauthorized modifications, leaving systems vulnerable to attacks that could alter the BIOS and potentially compromise the entire system, such as rootkits and firmware viruses. Added to that, the traditional BIOS operates in 16-bit real mode, a constraint that limits the amount of code and memory it can address. This limitation hinders the performance and complexity of firmware, making it less suitable for modern computing needs [33]. Additionally, BIOS relies on the Master Boot Record (MBR) partitioning scheme, which supports a maximum disk size of 2 terabytes and allows only four primary partitions [40][95]. This constraint has become a significant drawback as storage capacities have increased. Furthermore, the traditional BIOS has limited flexibility and is challenging to update or extend. This inflexibility restricts the ability to support new hardware and technologies efficiently [14][1].

### 1.2 Modern BIOS and UEFI

### 1.2.1 Transition from traditional BIOS to UEFI (Unified Extensible Firmware Interface)

All the limitations listed earlier caused a transition to a more modern firmware interface, designed to address the shortcomings of the traditional BIOS. This section delves into the historical context of this shift, the driving factors behind it, and the advantages UEFI offers over the traditional BIOS.

The development of UEFI began in the mid-1990s as part of the Intel Boot Initiative, which aimed to modernize the boot process and overcome the limitations of the traditional BIOS. By 2005, the Unified EFI Forum, a consortium of technology companies including Intel, AMD, and Microsoft, had formalized the UEFI specification [40]. UEFI was designed to address the shortcomings of the traditional BIOS, providing several key improvements.

Figure 1.3: The UEFI logo (public domain, 2010)

One of the most significant advancements of UEFI is its support for 32-bit and 64-bit modes, allowing it to address more memory and run more complex firmware programs. This capability enables UEFI to handle the increased demands of modern hardware and software [33][97]. Additionally, UEFI uses the GUID Partition Table (GPT) instead of the MBR, supporting disks larger than 2 terabytes and allowing for a nearly unlimited number of partitions [34][95].

Improved boot performance is another driving factor. UEFI provides faster boot times compared to the traditional BIOS, thanks to its efficient hardware and software initialization processes. This improvement is particularly beneficial for systems with complex hardware configurations, where quick boot times are essential [33]. UEFI's modular architecture makes it more extensible and easier to update compared to the traditional BIOS. This design allows for the addition of drivers, applications, and other components without requiring a complete firmware overhaul, providing greater flexibility and adaptability to new technologies [1]. UEFI also includes enhanced security features such as *Secure Boot*, which ensures that only trusted software can be executed during the boot process, thereby protecting the system from unauthorized modifications and malware [14][23].

The industry-wide support and standardization of UEFI have accelerated its adoption across various platforms and devices. Major industry players, including Intel, AMD, and Microsoft, have adopted UEFI as the new standard for firmware interfaces, ensuring broad compatibility and interoperability [40].

#### 1.2.2 An other way with *coreboot*

While UEFI has become the dominant firmware interface for modern computing systems, it is not without its critics. Some of the primary concerns about UEFI include its complexity, potential security vulnerabilities, and the degree of control it provides to hardware manufacturers over the boot process. Originally known as LinuxBIOS, coreboot, is a free firmware project initiated in 1999 by Ron Minnich and his team at the Los Alamos National Laboratory. The project's primary goal was to create a fast, lightweight, and flexible firmware solution that could initialize hardware and boot operating systems quickly, while remaining transparent and auditable[89]. As an alternative to UEFI, coreboot offers a different approach to firmware that aims to address some of these concerns and continue the evolution of BIOS.

One of the main advantages of *coreboot* over UEFI is its simplicity, as it is designed to perform only the minimal tasks required to initialize hardware and pass control to a payload, such as a bootloader or operating system kernel. This minimalist approach reduces the attack surface and potential for security vulnerabilities, as there is less code that could be exploited by malicious actors [94]. Another significant benefit of *coreboot* is its libre nature. Unlike UEFI, which is controlled by a consortium of hardware and software vendors, *coreboot*'s source code is freely available and can be audited, modified, and improved by anyone. This transparency ensures that security researchers and developers can review the code for potential vulnerabilities and contribute to its improvement, fostering a community-driven approach to firmware development[89]. This project also supports a wide range of bootloaders, called payloads, allowing users to customize their boot process to suit their specific needs. Popular payloads include SeaBIOS, which provides legacy BIOS compatibility, and Tianocore, which offers UEFI functionality within the *coreboot* framework. This flexibility allows *coreboot* to be used in a variety of environments, from embedded systems to high-performance servers [88].

Figure 1.4: The coreboot logo, by Konsult Stuge & coresystems (coreboot logo license, 2008)

Despite its advantages, *coreboot* is not without its challenges. The project relies heavily on community contributions, and support for new hardware often lags behind that of UEFI. Additionally, the minimalist design of *coreboot* means that some advanced features provided by UEFI are not available by default. However, the *coreboot* community continues to work on adding new features and improving compatibility with modern hardware or security issues [75]. For example, it provides a *verified boot* function, allowing to prevent rootkits and other attacks based on firmware modifications [87]. However, it's important to note that *coreboot* is not entirely free in all aspects. Many modern processors and chipsets require *proprietary blobs*, short for *Binary Large Object*, which is a collection of binary data stored as a single entity. These blobs are necessary for *coreboot* to function correctly on a wide range of hardware, but they compromise the goal of having a fully free firmware one day [69], since these blobs are used for certain functionalities such as memory initialization and hardware management.

Figure 1.5: The GNU Boot logo, by Jason Self (CC0, 2020)

To address these concerns, the GNU Project has developed GNU Boot, a fully free distribution of firmware, including *coreboot*, that aims to be entirely free by avoiding the use of proprietary binary blobs. GNU Boot is committed to using only free software for all aspects of firmware, making it a preferred choice for users and organizations that prioritize software freedom and transparency [70].

### 1.3 Shift in firmware responsibilities

Initially, the BIOS's primary function was to perform the POST, a basic diagnostic testing process to check the system's hardware components and ensure they were functioning correctly. This included verifying the CPU, memory, and essential peripherals before passing control to the operating system's bootloader. This process was relatively simple, given the limited capabilities and straightforward architecture of early computer systems [14]. As computer systems advanced, particularly with the advent of more sophisticated memory technologies, the role of firmware expanded significantly. Modern memory modules operate at much higher speeds and capacities than their predecessors, requiring precise configuration to ensure stability and optimal performance. Firmware now plays a critical role in managing the memory controller, which is responsible for regulating data flow between the processor and memory modules. This includes configuring memory frequencies, voltage levels, and timing parameters to match the specifications of the installed memory [40][9]. Beyond memory management, firmware responsibilities have broadened to encompass a wide range of system-critical tasks, and even so by including runtime components in addition to its initialization tasks. One key area is power management, where firmware is responsible for optimizing energy consumption across various components of the system. Efficient power management is essential not only for extending battery life in portable devices but also for reducing thermal output and ensuring system longevity in desktop and server environments. Moreover, modern firmware takes on significant roles in hardware initialization and configuration, which were traditionally handled by the operating system. For example, the initialization of USB controllers, network interfaces, and storage devices is now often managed by the firmware during the early stages of the boot process. This shift ensures that the operating system can seamlessly interact with hardware from the moment it takes control, reducing boot times and improving overall system reliability [40]. Security has also become a paramount concern for modern firmware. UEFI (Unified Extensible Firmware Interface), which has largely replaced traditional BIOS in modern systems, includes features which prevents unauthorized or malicious software from loading during the boot process. This helps protect the system from rootkits and other low-level malware that could compromise the integrity of the operating system before it even starts [40]. In the context of performance tuning, firmware sometimes also plays a key role in enabling and managing overclocking, particularly for the memory subsystem. By allowing adjustments to memory frequencies, voltages, and timings, firmware provides tools for enthusiasts to push their systems beyond default limits. At the same time, it includes safeguards to manage the risks of instability and hardware damage, balancing performance gains with system reliability [14].

In summary, the evolution of firmware from simple hardware initialization routines to complex management systems reflects the increasing sophistication of modern computer architectures. Firmware is now a critical layer that not only ensures the correct functioning of hardware components but also optimizes performance, manages power consumption, and enhances system security, making it an indispensable part of contemporary computing.

This document will focus on *coreboot* during the next parts to study how modern firmware interact with hardware and also as a basis for improvements.

### Chapter 2

# Characteristics of ASUS KGPE-D16 mainboard

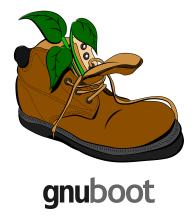

Figure 2.1: The KGPE-D16 (CC BY-SA 4.0, 2021)

### 2.1 Overview of ASUS KGPE-D16 hardware

The ASUS KGPE-D16 server mainboard is a dual-socket motherboard designed to support AMD Family 10h/15h series processors. Released in 2009, this mainboard was later awarded the *Respects Your Freedom* (RYF) certification in March 2017, underscoring its commitment to fully free software compatibility [43]. Indeed, this mainboard can be operated with a fully free firmware such as GNU Boot [71].

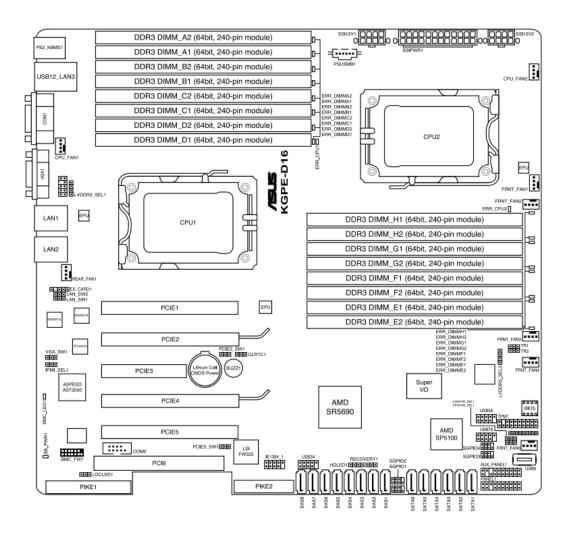

This mainboard is equipped with robust hardware components designed to meet the demands of high-performance computing. It features 16 DDR3 DIMM slots, capable of supporting up to 256GB of memory, although certain configurations may be limited to 192GB, with some reports suggesting the potential to support 256GB under specific conditions. In terms of expandability, the KGPE-D16 includes multiple PCle slots, with five physical slots available, although only four can be used simultaneously due to slot sharing. For storage, the mainboard provides several SATA ports. Networking capabilities are enhanced by integrated dual gigabit Ethernet ports, which provide high-speed connectivity essential for data-intensive tasks and network communication [16]. Additionally, the board is equipped with various peripheral interfaces, including USB ports, audio outputs, and other I/O ports, ensuring compatibility with a wide range of external devices.

Figure 2.2: Basic schematics of the ASUS KGPE-D16 Mainboard, ASUS (2011)

The physical layout of the ASUS KGPE-D16 is meticulously designed to optimize airflow, cooling, and power distribution. All of this is critical for maintaining system stability, particularly under heavy computational loads, as this board was designed for server operations. In particular, key components such as the CPU sockets, memory slots, and PCIe slots are strategically positioned.

Figure 2.3: The KGPE-D16, viewed from the top (CC BY-SA 4.0, 2024)

### 2.2 Chipset

Before diving into the specific components, it is essential to understand the roles of the northbridge and southbridge in traditional motherboard architecture. These chipsets historically managed communication between the CPU and other critical components of the system [3].

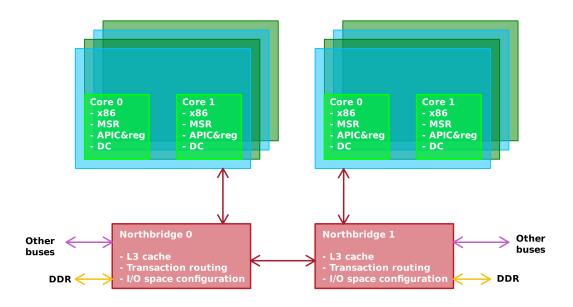

The northbridge is a chipset on the motherboard that traditionally manages high-speed communication between the CPU, memory (RAM), and graphics card (if applicable). It serves as a hub for data that needs to move quickly between these components. On the ASUS KGPE-D16, the functions typically associated with the northbridge are divided between the CPUs internal northbridge and an external SR5690 northbridge chip. The SR5690 specifically acts as a translator and switch, handling the HyperTransport interface, a high-speed communication protocol used by AMD processors, and converting it to ALink and PCle interfaces, which are crucial for connecting peripherals like graphics cards [12]. Additionally, the northbridge on the KGPE-D16 incorporates the IOMMU (Input-Output Memory Management Unit), which is crucial for ensuring secure and efficient memory access by I/O devices. The IOMMU allows for the virtualization of memory addresses, providing device isolation and preventing unauthorized memory access, which is particularly important in environments that run multiple virtual machines [3][128].

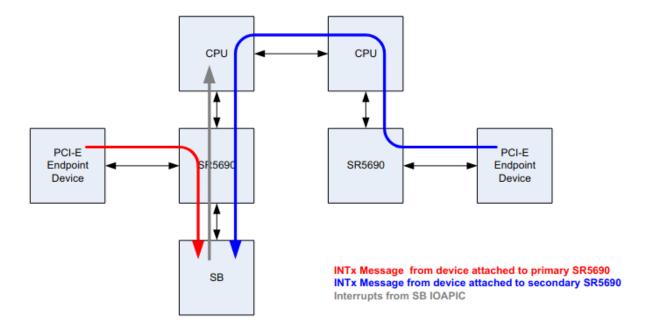

The southbridge, on the other hand, is responsible for handling lower-speed, peripheral interfaces such as the PCI, USB, and IDE/SATA connections, as well as managing onboard audio and network controllers. On the KGPE-D16, these functions are managed by the SP5100 southbridge chip, which integrates several critical functions including the LPC bridge, SATA controllers, and other essential I/O operations [3][131]. It is essentially an ALink bus controller and includes the hardware interrupt controller, the IOAPIC. Interrupts from peripheral always pass through the northbridge (fig. 2.4), since it translates ALink to HyperTransport for the CPUs and contains the IOMMU [12].

Figure 2.4: Functional diagram presenting the IOAPIC function of the SP5100, ASUS (2011)

In addition to the northbridge and southbridge, the KGPE-D16 also contains specialized chips for managing input/output operations and system health monitoring. The WINBOND W83667HG-A Super I/O chip handles traditional I/O functions such as legacy serial and parallel ports, keyboard, and mouse interfaces, but also the SPI chip (Serial Peripheral Interface, a synchronous serial communication protocol primarily used to communicate between microcontrollers and peripheral devices like sensors or memory devices) that contains the firmware [135]. Meanwhile, the Nuvoton W83795G/ADG Hardware Monitor oversees the systems health by monitoring temperatures, voltages, and fan speeds, ensuring that the system operates within safe parameters [79]. On the KGPE-D16, access to the Super I/O from a CPU core is done through the SR5690, then the SP5100, as that can be observed on the functional diagram of the chipset (fig. 2.5) [12].

Figure 2.5: Functional diagram of the KGPE-D16 chipset (CC BY-SA 4.0, 2024)

### 2.3 Processors

The ASUS KGPE-D16 supports AMD Family 10h processors, but it is important to note that Vikings, a known vendor for libre-software-compatible hardware, does not recommend using the Opteron 6100 series due to the lack of IOMMU support, which is critical for security. Fortunately, AMD Family 15h processors are also supported. However, the Opteron 6300 series, while supported, requires proprietary microcode updates for stability, IOMMU functionality, and fixes for specific vulnerabilities, including a gain-root- via-NMI exploit. The Opteron 6200 series does not suffer from these problems and works properly without any proprietary microcode update needed [111].

Figure 2.6: Annotated photography of an Opteron 6200 series CPU (2024), from a photography by AMD Inc. (2008)

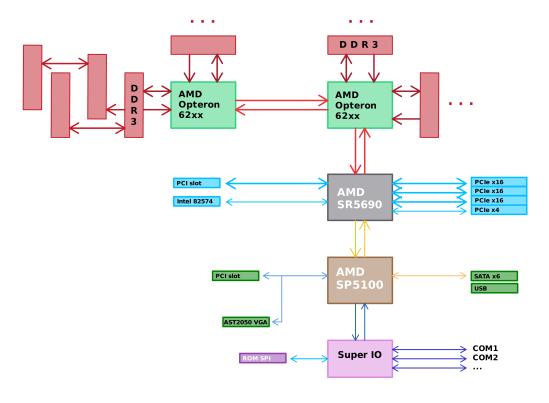

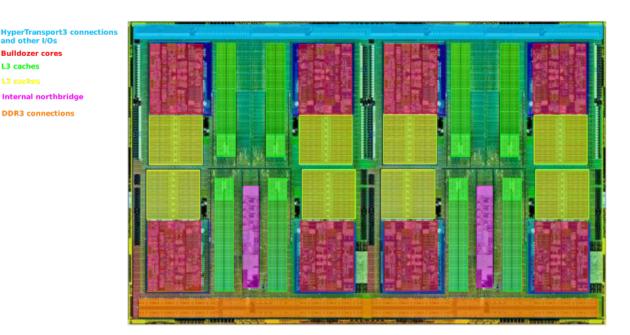

The Opteron 6200 series, part of the Bulldozer microarchitecture, was designed to target high-performance server applications. These processors feature 16 cores, organized into 8 Bulldozer modules, with each module containing two integer cores that shared resources like the floating-point unit (FPU) and L2 cache (fig. 2.6, 2.7) [7][96]. The architecture of the Opteron 6200 series is built around AMD's Bulldozer core design, which uses Clustered Multithreading (CMT) to maximize resource utilization. This is a technique where each processor module contains two integer cores that share certain resources like the floating-point unit (FPU), L2 cache, and instruction fetch/decode stages. Unlike traditional multithreading, where each core handles multiple threads, CMT allows two cores to share resources to improve parallel processing efficiency. This approach aims to balance performance and resource usage, particularly in multi- threaded workloads, though it can lead to some performance trade-offs in single-threaded tasks. In the Opteron 6272, the processor consists of eight modules, effectively creating 16 integer cores. Due to the CMT architecture, each Opteron 6272 chip functions as two CPUs within a single processor, each with its own set of cores, L2 caches, and shared L3 cache. Here, one CPU is made by four modules, each module in it sharing certain components, such as the FPU and L2 cache, between two integer cores. The L3 cache is shared across these modules. HyperTransport links provide high-speed communication between the two sockets of the KGPE-D16. Shared L3 cache and direct memory access are provided by each socket [7][52].

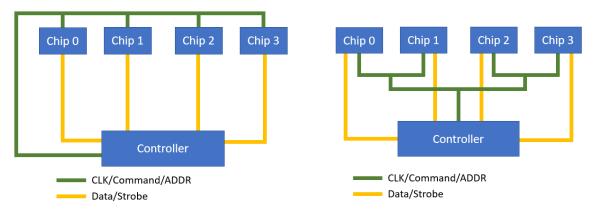

This architecture also integrates a quad-channel DDR3 memory controller directly into the processor die, which facilitates high bandwidth and low latency access to memory. This memory controller supports DDR3 memory speeds up to 1600 MHz and connects directly to the memory modules via the memory bus. By integrating the memory controller into the processor, the Opteron 6200 series reduces memory access latency, enhancing overall performance [7][6]. It is interesting to note that Opterons incorporate the internal northbridge that we cited previously. The traditional northbridge functions, such as memory controller and PCIe interface management, are partially integrated into the processor. This integration reduces the distance data must travel between the CPU and memory, decreasing latency and improving performance, particularly in memory-intensive applications [7].

Figure 2.7: Functional diagram of an Opteron 6200 package (CC BY-SA 4.0, 2024)

Power efficiency was a key focus in the design of the Opteron 6200 series. Despite the high core count, the processor includes several power management features, such as Dynamic Power Management (DPM) and Turbo Core technology. These features allow the processor to adjust power usage based on workload demands, balancing performance with energy consumption. However, the Bulldozer architecture's focus on high clock speeds and multi-threaded performance resulted in higher power consumption compared to competing architectures [96]. A special model of the series, called *high efficiency* models, solve a bit this problem by proposing a bit less performant processor but with a power consumption divided by a factor from 1.5 to 2.0 in some cases.

The processor connected to the I/O hub is known as the Bootstrap Processor (BSP). The BSP is responsible for starting up the system by executing the initial firmware code from the reset vector, a specific memory address where the CPU begins execution after a reset [4]. Core 0 of the BSP, called the Bootstrap Core (BSC), initiates this process. During early initialization, the BSP performs several critical tasks, such as memory initialization, and bringing other CPU cores online. One of its duties is storing Built-In Self-Test (BIST) information, which involves checking the integrity of the processor's internal components to ensure they are functioning correctly. The BSP also determines the type of reset that has occurred whether it's a cold reset, which happens when the system is powered on from an off state, or a warm reset, which is a restart without turning off the power. Identifying the reset type is crucial for deciding which initialization procedures need to be executed [4][9].

### 2.4 Baseboard Management Controller

The Baseboard Management Controller (BMC) on the KGPE-D16 motherboard, specifically the ASpeed AST2050, plays a role in the server's architecture by managing out-of-band communication and control of the hardware. The AST2050 is based on an ARM926EJ-S processor, a low-power 32-bit ARM architecture designed for embedded systems [102]. This architecture is well-suited for BMCs due to its efficiency and capability to handle multiple management tasks concurrently without significant resource demands from the main system.

The AST2050 features several key components that contribute to its functionality. It includes an integrated VGA controller, which enables remote graphical management through KVM-over-IP (Keyboard, Video, Mouse), a critical feature for administrators who need to interact with the system remotely, including BIOS updates and troubleshooting [100]. Additionally, the AST2050 integrates a dedicated memory controller, which supports up to 256MB of DDR2 RAM. This allows it to handle complex tasks and maintain responsiveness during management

operations [36]. The BMC also features a network interface controller (NIC) dedicated to management traffic, ensuring that remote management does not interfere with the primary network traffic of the server. This separation is vital for maintaining secure and uninterrupted system management, especially in environments where uptime is critical [103]. Another important architectural aspect of the AST2050 is its support for multiple I/O interfaces, including I2C, GPIO, UART, and USB, which allow it to interface with various sensors and peripherals on the motherboard [104]. This versatility enables comprehensive monitoring of hardware health, such as temperature sensors, fan speeds, and power supplies, all of which can be managed and configured through the BMC.

When combined with OpenBMC [129], a libre firmware that can be run on the AST2050 thanks to Raptor Engineering [90], the architecture of the BMC becomes even more powerful. OpenBMC takes advantage of the AST2050's architecture, providing a flexible and customizable environment that can be tailored to specific use cases. This includes adding or modifying features related to security, logging, and network management, all within the BMC's ARM architecture framework [57].

### Chapter 3

### Key components in modern firmware

#### 3.1 General structure of coreboot

The firmware of the ASUS KGPE-D16 is crucial in ensuring the proper functioning and optimization of the mainboard's hardware components. In this chapter and for the rest of this document, we're basing our study on the 4.11 version of *coreboot* [27], which is the last version that supported the ASUS KGPE-D16 mainboard.

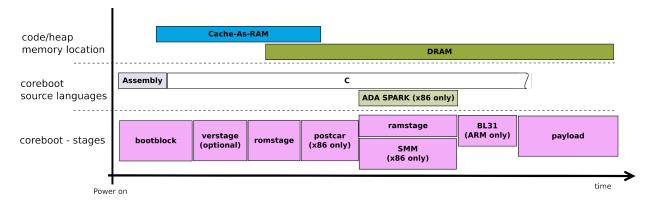

For the initialization tasks to be done efficiently, coreboot is organized in different stages (fig. 3.1) [87].

Figure 3.1: coreboot's stages timeline, by coreboot project (CC BY-SA 4.0, 2009)

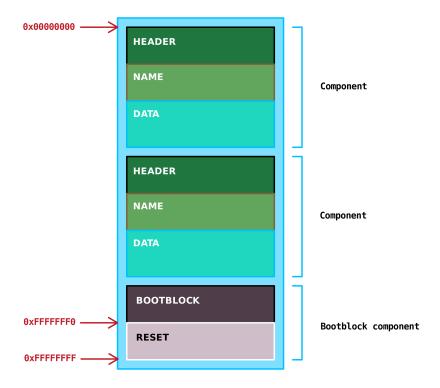

Being a complex project with ambitious goals, *coreboot* decided early on to establish an file-system-based architecture for its images (also called ROMs). This special file-system is CBFS (which stands for coreboot file system). The CBFS architecture consists of a binary image that can be interpreted as a physical disk, referred to here as ROM. A number of independent components, each with a header added to the data, are located within the ROM. The components are nominally arranged sequentially, although they are aligned along a predefined boundary (fig. 3.2).

Each stage is compiled as a separate binary and inserted into the CBFS with custom compression. The bootblock stage is usually not compressed, while the ramstage and the payload are compressed with LZMA. Each stage loads the next stage at a given address (possibly decompressing it in the process).

Some stages are relocatable and can be placed anywhere in the RAM. These stages are typically cached in the CBMEM for faster loading times during wake-up. The CBMEM is a specific memory area used by the *coreboot* firmware to store important data structures and logs during the boot process. This area is typically allocated in the system's RAM and is used to store various types of runtime information that it might need to reference after the initial boot stages.

In general, *coreboot* manages main memory through a structured memory map (fig. 3.1), allocating specific address ranges for various hardware functions and system operations. The first 640KB of memory space is typically unused by coreboot due to historical reasons. Graphics-related operations use the VGA address range and the text mode address ranges. It also reserves the higher for operating system use, ensuring that critical system components like the IOAPIC and TPM registers have dedicated address spaces. This structured approach

helps maintain system stability and compatibility across different platforms and allows for a reset vector fixed at an address (0xFFFFFFF0), regardless of the ROM size. Payloads are typically loaded into high memory, above the reserved areas for hardware components and system resources. The exact memory location can vary depending on the system's configuration, but generally, payloads are placed in a region of memory that does not conflict with the firmware code or the reserved memory map areas, such as the ROM mapping ranges. This placement ensures that payloads have sufficient space to execute without interfering with other critical memory regions allocated [26].

| 0x00000-0x9FFFF          | Low memory (first 640KB). Never used.       |

|--------------------------|---------------------------------------------|

| OxAOOOO-OxAFFFF          | VGA graphics address range.                 |

| 0xB0000-0xB7FFF          | Monochrome text mode address range. Few     |

|                          | motherboards use it, but the KGPE-D16 does. |

| 0xB8000-0xBFFFF          | Text mode address range.                    |

| 0xFEC00000               | IOAPIC address.                             |

| 0xFED44000-0xFED4FFFF    | Address range for TPM registers.            |

| 0xFF000000-0xFFFFFFF     | 16 MB ROM mapping address range.            |

| 0xFF800000-0xFFFFFFF     | 8 MB ROM mapping address range.             |

| 0xFFC00000-0xFFFFFFF     | 4 MB ROM mapping address range.             |

| OxFECOOOOO-DEVICEMEMHIGH | Reserved area for OS use.                   |

Table 3.1: coreboot memory map

#### 3.1.1 Bootblock

The bootblock is the first stage executed after the CPU reset. The beginning of this stage is written in assembly language, and its main task is to set everything up for a C environment. The rest, of course, is written in C. This stage occupies the last 20k (fig. 3.2) of the image and within it is a main header containing information about the ROM, including the size, component alignment, and the offset of the start of the first CBFS component. This block is a mandatory component as it also contains the entry point of the firmware.

Figure 3.2: coreboot ROM architecture (CC BY-SA 4.0, 2024)

Upon startup, the first responsibility of the bootblock is to execute the code from the reset vector located at

the conventional reset vector in 16-bit real mode. This code is specific to the processor architecture and, for our board, is stored in the architecture-specific sources for x86 within *coreboot*. The entry point into *coreboot* code is defined in two files in the src/cpu/x86/16bit/ directory: reset16.inc and entry16.inc. The first file serves as a jump to the \_start16bit procedure defined in the second. Due to space constraints this function must remain below the 1MB address space because the IOMMU has not yet been configured to allow anything else.

During this early initialization, the Bootstrap Core (BSC) performs several critical tasks while the other cores remain dormant. These tasks include saving the results (and displaying them if necessary) of the Built-in Self-Test (BIST), formerly known as POST; invalidating the TLB to prevent any address translation errors; determining the type of reset (e.g., cold start or warm start); creating and loading an empty Interrupt Descriptor Table (IDT) to prevent the use of "legacy" interrupts from real mode until protected mode is reached. In practice, this means that at the slightest exception, the BSC will halt. The code then switches to 32-bit protected mode by mapping the first 4 GB of address space for code and data, and finally jumps to the 32-bit reset code labeled \_protected\_start.

Once in protected mode, which constitutes the "normal" operating mode for the processor, the next step is to set up the execution environment. To achieve this, the code contained in src/cpu/x86/32bit/entry32.inc, followed by src/cpu/x86/64bit/entry64.inc, and finally src/arch/x86/bootblock\_crt0.S, establishes a temporary stack, transitions to long mode (64-bit addressing) with paging enabled, and sets up a proper exception vector table. The execution then jumps to chipset-specific code via the bootblock\_pre\_c\_entry procedure. Once these steps are completed, the bootblock has a minimal C environment. The procedure now involves allocating memory for the BSS, and decompressing and loading the next stage.

The jump to \_bootblock\_pre\_entry leads to the code files src/soc/amd/common/block/cpu/car/cache\_as\_ram.S and src/vendorcode/amd/agesa/f15tn/gcccar.inc, which are specific to AMD chipsets. It's worth noting that these files were developed by AMD's engineers as part of the AGESA project. The operations performed at this stage are related to pre-RAM memory initialization. All cores of all processors (up to a limit of 64 cores) are started. The Cache-As-Ram is configured using the Memory-type range registers. These registers allow the specification of a specific configuration for a given memory area [9]. In this case, the area that should correspond to physical memory is mapped to the cache, while other areas, such as PCI or other bus zones, are configured accordingly. A specific stack is set up for each core of each processor (within the arbitrary limit of 64 cores and 7 nodes, meaning 7 Core 0s). Core 0s receive 16KB, while the Bootstrap Core (BSC) gets 64KB. The other cores receive 4KB each. All cores except the BSC are halted and will restart during the romstage. Finally, the execution jumps to the entry point of the bootblock written in C, labeled bootblock\_c\_entry. This entry point is located in src/soc/amd/stoneyridge/bootblock/bootblock.c and is specific to AMD processors. It is the first C routine executed, and its role is to verify that the current processor is indeed the BSC, allowing the function bootblock\_main\_with\_basetime to be called exclusively by the BSC.

We are now in the file src/lib/bootblock.c, written by Google's team, and entering the bootblock\_main\_with\_basetime function, which immediately calls bootblock\_main\_with\_timestamp. At this stage, the goal is to start the romstage, but a few more tasks need to be completed.

The bootblock\_soc\_early\_init function is called to initialize the I2C bus of the southbridge. The bootblock\_fch\_early\_init function is invoked to initialize the SPI buses (Serial Peripheral Interface, allowing to access the chip that contains the ROM) and the serial and "legacy" buses of the southbridge. The CMOS clock is then initialized, followed by the pre-initialization of the serial console. The code then calls the bootblock\_mainboard\_init function, which enters, for the first time, the files specific to the ASUS KGPE-D16 motherboard: src/mainboard/ASUS/kgpe-d16/bootblock.c. This code performs the northbridge initialization via the bootblock\_northbridge\_init function found in src/northbridge/amd/amdfam10/bootblock.c. This involves locating the HyperTransport bus and enabling the discovery of devices connected to it (e.g., processors). The southbridge is initialized using the bootblock\_southbridge\_init function from src/southbridge/amd/sb700/bootblock.c. This function, largely programmed by Timothy Pearson from Raptor Engineering, who performed the first coreboot port for the ASUS KGPE-D16, finalizes the activation of the SPI bus and the connection to the ROM memory via SuperIO. The state of a recovery jumper is then checked (this jumper is intended to reset the CMOS content, although it is not fully functional at the moment, as indicated by the FIXME comment in the code). Control then returns to bootblock\_main in src/lib/bootblock.c.

At this point, everything is ready to enter the romstage. *coreboot* has successfully started and can now continue its execution by calling the run\_romstage function from src/lib/prog\_loaders.c. This function begins by locating the corresponding segment in the ROM via the southbridge and SPI bus using prog\_locate, which utilizes the SPI driver in src/drivers/cbfs\_spi.c. The contents of the romstage are then copied into the cache-as-ram by cbfs\_prog\_stage\_load. Finally, the prog\_run function transitions to the romstage after switching back to 32-bit mode.

#### 3.1.2 Romstage

The *romstage* in *coreboot* serves the critical function of early initialization of peripherals, particularly system memory. This stage is crucial for setting up the necessary components for the platform's operation, ensuring that everything is in place for subsequent stages of the boot process. During this phase, *coreboot* configures the Advanced Programmable Interrupt Controller (APIC), which is responsible for correctly handling interrupts across multiple CPUs, especially in systems using Symmetric Multiprocessing (SMP). This includes setting up the Local APIC on each processor and the IOAPIC, part of the southbridge, to ensure that interrupts from peripherals are routed to the appropriate CPUs. Additionally, the firmware configures the HyperTransport (HT) technology, a high-speed communication protocol that facilitates data exchange between the processor and the northbridge, ensuring smooth data flow between these components. During this stage, microcode patches may be loaded into CPU and remain resident, settings related to memory controllers and CPU too.

The romstage begins with a call to the \_start function, defined in src/cpu/x86/32bit/entry32.inc via src/arch/x86/assembly\_entry.S. We then enter the cache\_as\_ram\_setup procedure, written in assembly language, located in src/cpu/amd/car/cache\_as\_ram.inc. This procedure configures the cache to load the future ramstage and initialize memory based on the number of processors and cores present. Once this is completed, the code calls cache\_as\_ram\_main in src/mainboard/asus/kgpe-d16/romstage.c, which serves as the main function of the romstage. In the cache\_as\_ram\_main function, after reducing the speed of the HyperTransport bus, only the Bootstrap Core (BSC) initializes the spinlocks for the serial console, the CMOS storage memory (used for saving parameters), and the ROM. At this point, the HyperTransport bus is enumerated, and the PCI bridges are temporarily disabled. The port 0x80 of the southbridge, used for motherboard debugging with Post Codes, is also initialized. These codes indicate the status of the boot process and can be displayed using special PCI cards connected to the system. The SuperIO is then initialized to activate the serial port, allowing the serial console to follow coreboots progress in real-time. If everything proceeds as expected, the code 0x30 is sent, and the boot process continues.

If the result of the Built-in Self-Test (BIST), saved during the bootblock, shows no anomalies, all cores of all nodes are configured, and they are placed back into sleep mode (except for the Core 0s). If everything goes well, the code 0x32 is sent, and the process continues. Using the enable\_sr5650\_dev8 function, the southbridges P2P bridge is activated. Additionally, a check is performed to ensure that the number of physical processors detected does not exceed the number of sockets available on the board. If any issues were detected during the BIST, the machine will halt, and the error will be displayed on the console. Otherwise, the process continues, and the default hardware information table is constructed, and the microcode of the physical processors is updated if necessary. If everything proceeds correctly, the code 0x33 and then 0x34 is sent, and the process continues. The information about the physical processors is retrieved using amd\_ht\_init, and communication between the two sockets is configured via amd\_ht\_fixup. This process includes disabling any defective HT links (one per socket in this AMD Family 15h chipset). If everything is working as expected, the code 0x35 is sent, and the boot process continues. With the finalize\_node\_setup function, the PCI bus is initialized, and a mapping is created (setup\_mb\_resource\_map). If all goes well, the code 0x36 is sent. This is done in parallel across all Core Os, so the system waits for all cores to finish using the wait\_all\_coreO\_started function. The communication between the northbridge and southbridge is prepared using sr5650\_early\_setup and sb7xx\_51xx\_early\_setup, followed by the activation of all cores on all nodes, with the system waiting for all cores to be fully initialized. If everything is successful, the code 0x38 is sent.

At this point, the timer is activated, and a warm reset is performed via the soft\_reset function to validate all configuration changes to the HT, PCI buses, and voltage/power settings of the processors and buses. This results in a system reboot, passing again through the *bootblock*, but much faster this time since the system recognizes the warm reset condition. Once this reboot is complete, the HyperTransport bus is reconfigured into isochronous

mode (switching from asynchronous mode), finalizing the configuration process.

Memory training and optimization are also key functions of the firmware during the *romstage*. This process involves adjusting memory settings, such as timings, frequencies, and voltages, to ensure that the installed memory modules operate efficiently and stably. This step is crucial for achieving optimal performance, especially when dealing with large amounts of RAM and many CPU cores, as supported by the KGPE-D16. We'll see that in detail during the next chapter.

After memory initialization, the process returns to the cache\_as\_ram\_main function, where a memory test is performed. This involves writing predefined values to specific memory locations and then verifying that the values can be read back correctly. If everything passes successfully, the CBMEM is initialized and one sends code 0x41. At this point, the configuration of the PCI bus is prepared, which will be completed during the ramstage by configuring the PCI bridges. The system then exits cache\_as\_ram\_main and returns to cache\_as\_ram\_setup to finalize the process.

coreboot then transitions to the next stage, known as the postcar stage, where it exits the cache-as-RAM mode and begins using physical RAM.

### 3.1.3 Ramstage

The ramstage performs the general initialization of all peripherals, including the initialization of PCI devices, on-chip devices, the TPM (if not done by verstage), graphics (optional), and the CPU (setting up the System Management Mode). After this initialization, tables are written to inform the payload or operating system about the existence and current state of the hardware. These tables include ACPI tables (specific to x86), SMBIOS tables (specific to x86), coreboot tables, and updates to the device tree (specific to ARM). Additionally, the ramstage locks down the hardware and firmware by applying write protection to boot media, locking security-related registers, and locking SMM (specific to x86), which is a resident component in a protected area. [87]. CBMEM data structures (like coreboot tables, memory map, etc.) are populated during this stage and left resident for the OS or payload to access, same for SMBIOS tables, ACPI tables and eventually option ROMS.

Effective resource allocation is essential for system stability, particularly in complex configurations involving multiple CPUs and peripherals. This stage manages initial resource allocation, resolving any conflicts between hardware components to prevent resource contention and ensure smooth operation and security, which is a major concern in modern systems. This includes support for IOMMU, which is crucial for preventing unauthorized direct memory access (DMA) attacks, particularly in virtualized environments (however there are still vulnerabilities that can be exploited, such as sub-page or IOTLB-based attacks or even configuration weaknesses [74][72]).

#### 3.1.3.1 Advanced Configuration and Power Interface

The Advanced Configuration and Power Interface (ACPI) is a critical component of modern computing systems, providing an open standard for device configuration and power management by the operating system (OS). Developed in 1996 by Intel, Microsoft, and Toshiba, ACPI replaced the older Advanced Power Management (APM) standard with more advanced and flexible power management capabilities [31]. At its core, ACPI is implemented through a series of data structures and executable code known as ACPI tables, which are provided by the system firmware and interpreted by the OS at runtime. It means that these are components from the firmware that remain resident while the OS runs. These tables describe various aspects of the system, including hardware resources, device power states, and thermal zones. The ACPI Specification outlines these structures and provides the necessary standardization for interoperability across different platforms and operating systems [49]. These tables are used by the OS to perform low-level task, including managing power states of the CPU, controlling the voltage and frequency scaling (also known as Dynamic Voltage and Frequency Scaling, or DVFS), and coordinating power delivery to peripherals.

The ACPI Component Architecture (ACPICA) is the reference implementation of ACPI, providing a common codebase that can be used by OS developers to integrate ACPI support. ACPICA includes tools and libraries that allow for the parsing and execution of ACPI Machine Language (AML) code, which is embedded within the ACPI tables [86]. One of the key tools in ACPICA is the Intel ACPI Source Language (IASL) compiler, which converts ACPI Source Language (ASL) code into AML bytecode, allowing firmware developers to write custom

ACPI methods [29]. The triggering of ACPI events is managed through a combination of hardware signals and software routines. For example, when a user presses the power button on a system, an ACPI event is generated, which is then handled by the OS. This event might trigger the system to enter a low-power state, such as sleep or hibernation, depending on the configuration provided by the ACPI tables [49]. These power states are defined in the ACPI specification, with global states (G0 to G3) representing different levels of system power consumption, and device states (D0 to D3) representing individual device power levels.

The ASUS KGPE-D16 mainboard, which is designed for server and high-performance computing environments, needs ACPI for managing its power distribution across multiple CPUs and attached peripherals. ACPI is integral in controlling the power states of various components, thereby optimizing performance and energy use. Additionally, the firmware on the KGPE-D16 uses ACPI tables to manage system temperature and fan speed, ensuring reliable operation under heavy workloads [16].

### 3.1.3.2 System Management Mode

System Management Mode (SMM) is a highly privileged operating mode provided by x86 processors for handling system-level functions such as power management, hardware control, and other critical tasks that are to be isolated from the OS and applications. Introduced by Intel, SMM operates in an environment separate from the main operating system, offering a controlled space for executing sensitive operations [61]. This is another firmware component that remains resident while the OS runs.